Circuito sincronico de 2 bites con dos FF J-K que responde a las siguientes condiciones.

Ja= Bx Ka= Bx Jb= x KB = x

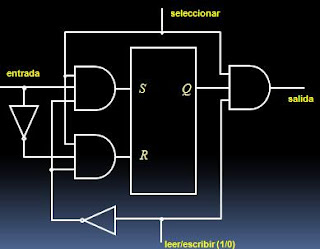

Celda de memoria. configurada en un FF RS modificado tipo D y con un inversor en la entrada de lectura escritura.

Diagrama de la celda de memoria de un bit indicando los cuatro conectores esenciales entrada, salida seleccionar y habilitador de lectura escritura

Unidad de Memoria de 4 x 3 bits, la selección de memoria la realiza el decodificador 2x4 a las salidas D1,D2,D3 y D4. Ingresa palabras de 3 bits y sale a traves de las tres compuertas or de cuatro entradas, la habilitación de lectura y escritura se realiza a todas las celdas de memoria.

Tabla de Verdad de la operación del decodificador indicando las combinaciones de las entradas A0 y A1

Unidad de memoria RAM las lineas de entrada y salida son n que representa el tipo de palabras. Están las líneas de dirección en función de k.

Direcciones de memoria de la unidad de memoria de 1024 x 16 bits, las direcciones de memoria van de 0 a 1023.

Celda de memoria RAM, tiene dos entradas tanto para B y B´ de igual forma para la salida.

Una unidad de memoria formada por n celdas llamada Memoria distribuida con proceso de lectura y proceso de escritura.

Buffer de tres estados; memoria intermedia de control de paso de información.

con solo bite

con dos bites y con tabla de verdad que indica el efecto de la accion de los habilitadores

memoria RAM de 16x 1 de 16 posiciones para las entradas de un bit.

Diseño de una memoria RAM usando celdas de cuatro bits para cuatro palabras seleccionadas por un decodificador.

Memoria de 64 Kbites con lectura y escritura de palabras de 16 bits.

yquehaydelaceldadememoriaSRAM,cómohagounaenELECTRONICWORKBENCH-YoenLOGISIM

ResponderEliminarNOPUEDESHACERUNAENELECTRONICWORKBENCHPORQUEALRETROALIMENTARLOSINVERSORESTESALEOKSUGESTION!

Eliminar